**Developer Note**

# Power Macintosh G3

Technical Publications © Apple Computer, Inc. 1998  Apple Computer, Inc.

© 1998 Apple Computer, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc., except to make a backup copy of any documentation provided on CD-ROM. Printed in the United States of America.

The Apple logo is a trademark of Apple Computer, Inc. Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

No licenses, express or implied, are granted with respect to any of the technology described in this book. Apple retains all intellectual property rights associated with the technology described in this book. This book is intended to assist application developers to develop applications only for Apple-labeled or Apple-licensed computers.

Every effort has been made to ensure that the information in this manual is accurate. Apple is not responsible for printing or clerical errors.

Apple Computer, Inc. 1 Infinite Loop Cupertino, CA 95014 408-996-1010

Apple, the Apple logo, FireWire, GeoPort, LaserWriter, LocalTalk, Macintosh, PlainTalk, and Power Macintosh are trademarks of Apple Computer, Inc., registered in the United States and other countries.

The FireWire logo and QuickDraw are trademarks of Apple Computer, Inc.

Adobe Illustrator, Acrobat, and PostScript are trademarks of Adobe Systems Incorporated, which may be registered in certain jurisdictions. Helvetica and Palatino are registered

trademarks of Linotype Company.

ITC Zapf Dingbats is a registered trademark of International Typeface Corporation.

PowerPC is a trademark of International Business Machines Corporation, used under license therefrom.

Simultaneously published in the United States and Canada.

ALL IMPLIED WARRANTIES ON THIS MANUAL, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF THE ORIGINAL RETAIL PURCHASE OF THIS PRODUCT.

Even though Apple has reviewed this manual, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty. Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

## Contents

| Preface   | About This Note 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Topics Described In This Note11Supplemental Reference Documents12PowerPC Microprocessor12Mac OS12Open Firmware13PCI Cards14ATA Devices14USB Devices14FireWire Interface15                                                                                                                                                                                                                                                                                                                                       |

| Chapter 1 | Introduction 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Power Macintosh G3 Computer Features18Features of the Enclosure20Front View of the Enclosure21Back View of the Enclosure22Access to the Interior23Optional Features25DVD-ROM and DVD MPEG2 Decode Card25Serial Modem Communications26Compatibility Issues26System Software26DMA Addresses and NewWorld Software26Machine Identification and NewWorld Software26No Graphics Support on MLB27No Built-in AV I/O Connectors27PCI Expansion Slots27Internal Storage Devices28RAM Expansion28No L2 Cache Expansion29 |

ATA-3 Drives29No SCSI Ports29Line Voltages29Monitor Power29No Video RAM Expansion30No LocalTalk Serial Ports30USB Ports and Devices30

#### Chapter 2 Architecture 31

32 **Block Diagram and Buses Main Components** 34 34 PowerPC G3 Microprocessor Memory Subsystem 34 Second-Level Cache 35 System ROM 35 35 System RAM Core ICs 35 Grackle Memory Controller and PCI Bridge IC 36 Paddington I/O Controller IC 37 **Burgundy Sound IC** 37 Cuda IC 38 **Graphics Controller IC** 38 **Display Memory** 39 **USB** Controller 39 FireWire Link Controller 40 **Optional Internal Modem** 40

#### Chapter 3 I/O Features 41

ADB Port42USB Ports43USB Connectors44Transfer Types Supported44USB Compatibility Issues45ADB Compatibility45

Serial Port Compatibility 45 Macintosh-To-Macintosh Connections 46 **USB Storage Devices** 46 **USB** Controller 46 Keyboard 46 **Keyboard Layout** 46 Keyboard and USB 47 Mouse 48 **FireWire Ports** 48 **FireWire Connector** 49 50 **Ethernet Port** Internal Modem 50 **Disk Drives** 51 Ultra DMA/33 Hard Disk Drive 52 Optional Ultra2 SCSI (LVD) Drive 52 ATAPI CD-ROM Drive 52 **Optional ATAPI Zip Drive** 53 **Optional DVD-ROM Drive** 53 Sound System 53 Sound Outputs 53 Sound Inputs 54 **Digitizing Sound** 54 Video Monitor Port 55 **Graphics** Card 55 56 Monitor Connector 57 **Monitor Adapter Monitor Sense Codes** 57 **Display Resolution Modes** 59 **Graphics Acceleration Display Modes** 61

Chapter 4 Expansion Features 63

RAM DIMMs64Mechanical Specifications64Presence Detect EEPROM65RAM Address Multiplexing65SDRAM Devices66

PCI Expansion Slots 66 The Modem Interface 67

#### Chapter 5 System Software 69

70 The New Approach What Has Changed 71 72 Features of the New Approach 72 Performance **RAM Footprint** 73 **User Experience** 73 **Data Structures and Files** 73 73 Compatibility **Boot ROM Contents** 74 **POST Code** 75 **Open Firmware** 75 Mac OS 'ndrv' Drivers 75 RTAS 76 Mac OS ROM Image File Contents 76 **Open Firmware Script** 77 77 **Trampoline Code** Mac OS ROM Image 77 NewWorld Boot Process 77 What Is Different 78 **Interrupt Handling** 79 79 **Outmoded Resources RAM Footprint** 79 RTAS 79 NV-RAM 80 80 NanoKernel Startup Disk Control Panel 80 81 Open Firmware and the Device Tree **Open Firmware and Startup Devices** 81 Interrupt Layout 82 Machine Identification 82

| Appendix A | Conventions and Abbreviations 85              |    |    |  |  |  |

|------------|-----------------------------------------------|----|----|--|--|--|

|            | Typographical Conventions<br>Abbreviations 85 |    | 85 |  |  |  |

|            | Index                                         | 89 |    |  |  |  |

## Figures and Tables

| Chapter 1 | Introduction                                                                            | 17                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Figure 1-1<br>Figure 1-2<br>Figure 1-3<br>Figure 1-4<br>Figure 1-5                      | Front view of the enclosure21Back view of the enclosure22Opening the side panel23Interior of the computer24Closing the side panel25                                                                                                      |

| Chapter 2 | Architecture                                                                            | 31                                                                                                                                                                                                                                       |

|           | Figure 2-1                                                                              | Main logic board block diagram 33                                                                                                                                                                                                        |

| Chapter 3 | I/O Features                                                                            | 41                                                                                                                                                                                                                                       |

|           | Figure 3-1<br>Figure 3-2<br>Figure 3-3<br>Figure 3-4                                    | ADB connector42ANSI keyboard layout47FireWire connector49Monitor connector56                                                                                                                                                             |

|           | Table 3-1<br>Table 3-2<br>Table 3-3<br>Table 3-4<br>Table 3-5<br>Table 3-6<br>Table 3-7 | ADB connector pin assignments43USB connector pin assignments44FireWire connector pin assignments49Monitor connector pin assignments56Monitor sense codes58Supported display resolutions59Supported graphics acceleration display modes61 |

| Chapter 4 | Expansion Fea                                                                           | atures 63                                                                                                                                                                                                                                |

|           | Table 4-1                                                                               | Address multiplexing modes for SDRAM DIMMs 65                                                                                                                                                                                            |

## About This Note

This developer note describes a new Macintosh computer. The computer is referred to as the Power Macintosh G3 throughout the developer note. Where necessary, the term "original Power Macintosh G3" is used to refer to the earlier models.

This note describes the features of the Power Macintosh G3 computer, the logic board architecture and expansion capabilities, and issues affecting compatibility.

This developer note is intended to help hardware and software developers design products that are compatible with the Macintosh products described here. If you are not already familiar with Macintosh computers or if you would simply like additional technical information, you may wish to read the related technical manuals listed in the section "Supplemental Reference Documents."

This note is published only in electronic form, as an  $Adobe^{TM} Acrobat^{TM} PDF$  (portable document format) file and in HTML for browsers that support frame sets. The file is available from two sources:

- on the World Wide Web at <http://developer.apple.com/techpubs/ hardware/hardware.html>

- on the Reference Library Edition of the Developer CD Series, which is distributed as part of the monthly mailing to registered developers

## Topics Described In This Note

The information is arranged in five chapters, an appendix, and an index:

Chapter 1, "Introduction," gives a summary of the features of the logic board in the Power Macintosh G3 computer, describes the physical appearance of the enclosure, and lists the available configurations and options. This chapter also includes a section describing compatibility issues that developers need to be aware of to take advantage of the features available with the Power Macintosh G3 computer.

- Chapter 2, "Architecture," describes the internal organization of the computer. It includes a functional block diagram and descriptions of the main components of the logic board.

- Chapter 3, "I/O Features," describes the built-in input/output (I/O) devices and the external I/O ports. It also describes the built-in support for external video monitors that can be used with the computer.

- Chapter 4, "Expansion Features," describes the expansion slots on the logic board and provides descriptions of the expansion modules.

- Chapter 5, "System Software," describes the system software that comes with the computer, with emphasis on the new Open Firmware features.

- Appendix A, "Conventions and Abbreviations," describes the typographical conventions and lists the abbreviations used in this note.

## Supplemental Reference Documents

For more information about the technologies mentioned in this developer note, you may wish to consult some of the references listed in the following sections.

#### PowerPC Microprocessor

For more information about the PowerPC<sup>™</sup> 750 microprocessor used in the Power Macintosh G3 computer, you may wish to refer to the standard reference, PowerPC 740/750 Microprocessor Implementation Definition Book IV. Information about the PowerPC 750 microprocessor is also available on the World Wide Web at

http://www.mot.com/SPS/PowerPC/index.html

and

http://www.chips.ibm.com/products/ppc/overview

#### Mac OS

For a description of the version of the Mac OS that comes with the new models, refer to the Apple Technical Note for Mac OS 8.5. The Technote is available on the Technote Web site at

http://developer.apple.com/technotes/index.html

You should also have copies of the relevant books describing the system software for Macintosh computers available in technical bookstores and on the World Wide Web at

http://developer.apple.com/techpubs/mac/mac.html

#### **Open Firmware**

The NewWorld software architecture implemented on the Power Macintosh G3 computer follows some of the standards defined by the Open Firmware IEEE 1274-1995 specification and the CHRP binding.

The primary Open Firmware reference is the IEEE 1275-1994 Standard for Boot (Initialization, Configuration) Firmware: Core Requirements and Practices. You can order that document electronically from the IEEE Standards Department web site at

http://standards.ieee.org/catalog/bus.html

or you can order it by mail from

IEEE Standards Department 445 Hoes Lane, P. O. Box 1331 Piscataway, NJ 08855-1331 Telephone 800-678-4333 (US), 908-562-5432 (International)

The basis for the bootinfo file format and its use are described the document PowerPC Microprocessor Common Hardware Reference Platform (CHRP) System binding to: IEEE Std 1275-1994 Standard for Boot (Initialization, Configuration) Firmware. A bootinfo file contains Open Firmware script, a description, information for individual operating systems, and icons, along with other information.

An introduction to Open Firmware as used with PCI expansion cards on the Macintosh computer is given in *Designing PCI Cards and Drivers for Power Macintosh Computers.*

Three Apple Technical Notes provide additional information about Open Firmware on the Macintosh computer. They are

TN 1061: Open Firmware, Part I, which introduces Forth programming and outlines a technique for debugging Open Firmware drivers. It is available on the Technote Web site at http://developer.apple.com/technotes/tn/tn1061.html

- TN 1062: Open Firmware, Part II, which describes the contents of an expansion ROM for Open Firmware and lists properties common to all device types. It is available on the Technote Web site at http://developer.apple.com/technotes/tn/tn1062.html

- TN 1044: Open Firmware, Part III, which describes a typical device tree. It is available on the Technote Web site at http://developer.apple.com/technotes/tn/tn1044.html

### **PCI** Cards

For information about PCI expansion cards, refer to *Designing PCI Cards and Drivers for Power Macintosh Computers.* The Power Macintosh G3 computer supports version 2.1 of the PCI standard.

If you're interested in taking advantage of the 3D graphics acceleration features available on the PCI graphics card, you should have a copy of 3D Graphics Programming With QuickDraw 3D.

#### **ATA Devices**

For the latest information about the Mac OS software for ATA devices, see ATA Software Guide and ATA Device 0/1 Software Developers Guide, available on the World Wide Web at:

http://developer.apple.com/techpubs/hardware/hardware.html

#### **USB** Devices

For more information about the Universal Serial Bus (USB) on the Macintosh computer, refer to Apple Computer's USB DDK API Reference. Information is also available on the World Wide Web, at

http://developer.apple.com/dev/usb/

For full specifications of the Universal Serial Bus, developers should refer to the USB Implementation Forum on the World Wide Web, at

http://www.usb.org/developers/index.html

## **FireWire Interface**

For additional information about the FireWire IEEE 1394 interface and the Apple APIs for FireWire software, refer to the resources available on the Apple FireWire Web site at

http://www.apple.com/firewire/

The IEEE 1394-1995 standard is available from the IEEE. Ordering information can be found on the World Wide Web at

http://www.ieee.org

You may also find useful information at the 1394 trade association's Web site at

http://www.1394ta.org/

#### CHAPTER 1

Introduction

The Power Macintosh G3 computer is a new computer with a higher speed CPU and system bus and several new built-in I/O features that allow customers to assemble powerful and versatile Macintosh configurations.

## **Power Macintosh G3 Computer Features**

Here is a list of the hardware features of the Power Macintosh G3 computer. The major features are described more fully later in this note.

- Microprocessor: PowerPC G3 microprocessor running at a clock frequency of 300 MHz, 350 MHz, or 400 MHz depending on model and configuration. For more information, see "PowerPC G3 Microprocessor" (page 34).

- **Cache:** 512 KB or 1 MB (depending on model and configuration) of the backside second-level (L2) cache on processor module. The backside cache runs at half the clock frequency of the microprocessor.

- **Processor system bus:** 64-bit wide data and 32-bit wide address, 100 MHz clock, supporting split address and data tenures.

- RAM: four DIMM slots for industry standard PC-100 SDRAM (synchronous dynamic access memory) DIMMs (dual inline memory modules). Maximum memory with all four slots occupied is 1024 MB. A minimum of 64 MB of RAM is installed in one of the slots. For more information, see "RAM DIMMs" (page 64).

- ROM: New World ROM-in-RAM implementation with 1 MB of boot ROM.

For additional information about the ROM, see "System ROM" (page 35) and "Boot ROM Contents" (page 74).

- Graphics acceleration: 2D and 3D hardware graphics acceleration using the ATI 3D RAGE 128 GL graphics controller on the 66 MHz 2D/3D accelerated graphics card. Software support through Macintosh QuickDraw 3D and QuickDraw 3D RAVE (rendering acceleration virtual engine) APIs. For more information, see "Graphics Card" (page 55).

- Sound: supports 16 bits/channel stereo input and output on built-in 3.5mm line-level stereo input and output jacks, one built-in speaker. For more information, see "Sound System" (page 53).

- Hard disk drives: one internal Ultra DMA/33 hard disk or Ultra2 SCSI (LVD) hard disk. For more information, see "Disk Drives" (page 51).

- Drive bays: three drive bays, one of which is occupied by an Ultra DMA/33 hard disk or an Ultra2 SCSI (LVD) hard disk. The other two bays are available for adding other devices connected to a PCI controller card. For more information, see "Disk Drives" beginning on page 51.

- CD-ROM drive: internal 24x-speed ATAPI CD-ROM drive.

- DVD-ROM drive: optional ATAPI DVD-ROM drive providing support for 32x-speed CD-ROM and 5x-speed DVD-ROM media, as well as DVD-Video playback with the DVD MPEG2 decode module. The DVD MPEG2 decode module is connected to the PCI graphics card.

- **Zip drive:** optional 100 MB ATAPI Zip drive. If the Zip drive option is not installed at the time of purchase, data and power connectors are provided to add an ATAPI Zip drive to the system.

- USB ports: two USB ports, described in "USB Ports" (page 28). The computer comes with a USB mouse and a USB keyboard that has two additional USB ports. The additional ports are described under "Keyboard and USB" (page 47).

- ADB port: one ADB port for ADB devices or ColorSync control of Apple monitors. For more information, see "ADB Port" (page 42).

- Ethernet: built in Ethernet port for 10Base-T and 100Base-TX operation with an RJ-45 connector. For more information, see "Ethernet Port" (page 50).

- **FireWire ports:** two IEEE-1394 high-speed serial FireWire ports, which support transfer rates of 100, 200, and 400 Mbps.

- **Modem:** optional Apple 56 Kbps modem. The modem supports K56flex and V.90 protocols. For more information, see "Internal Modem" (page 50).

- Keyboard: Apple USB keyboard with function keys and inverted-T cursor motion keys. The keyboard operates as a low-speed (1.5 Mbps) USB device. It also provides a bus-powered USB hub with two USB ports. For more information, see "Keyboard" (page 46).

- **Mouse:** Apple USB mouse operating as a low-speed (1.5 Mbps) USB device. For more information, see "Mouse" (page 48).

- PCI card expansion slots: three slots for 33 MHz, 32-bit or 64-bit, 12-inch PCI cards; one slot for a 66 MHz 32-bit PCI card, occupied by the accelerated graphics card. For more information, see "PCI Expansion Slots" (page 66).

- **Power switch:** soft power controlled from the Apple USB keyboard, an ADB keyboard, and the front power button.

- Voltage switch: can be set to either 115 for voltages of 90-132 V or 230 for voltages of 180-264 V, depending on the voltage where the computer is installed. The voltage selection must be set manually.

- **Fan speed control:** The speed of the fan is thermally controlled and is automatically set to the lowest possible speed to minimize noise. The fan speed varies according to the temperature inside the enclosure. This is a function provided by the fan and is not under software control.

- **Energy saving:** sleep, startup, and shutdown scheduling can be controlled with an Energy Saver control panel.

## Features of the Enclosure

The Power Macintosh G3 enclosure is a new design. The following sections show the exterior design and the interior of the computer.

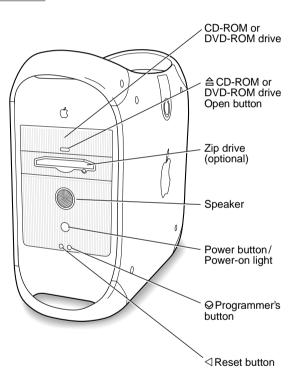

## Front View of the Enclosure

Figure 1-1 is a front view of the Power Macintosh G3 enclosure. The front view shows the openings for the CD/DVD-ROM drive and the optional ZIP drive, the speaker, the power button, the reset button, the NMI button, and the power-on light.

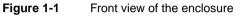

## Back View of the Enclosure

The back panel includes the A/C power socket, the monitor power socket, the I/O ports, and the openings for PCI cards.

Figure 1-2 shows the back view of the enclosure for the Power Macintosh G3 computer.

#### Figure 1-2 Back view of the enclosure

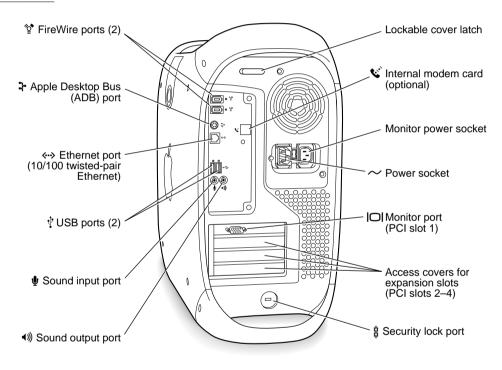

### Access to the Interior

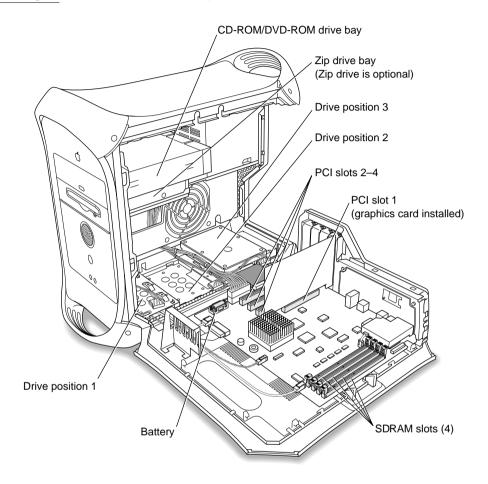

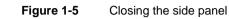

You can get access to the interior of the computer to add expansion RAM or PCI expansion cards by opening the side panel as shown in Figure 1-3. A view of the interior is shown in Figure 1-4. Figure 1-5 shows the proper way to close the side panel.

Figure 1-3 Opening the side panel

#### Figure 1-4 Interior of the computer

## **Optional Features**

Two features of the computer are implemented as plug-in modules available as a configuration option at the time of purchase.

## DVD-ROM and DVD MPEG2 Decode Card

The DVD-ROM drive configuration includes a DVD MPEG2 decode card module. That module does not occupy a PCI slot, but is attached to the accelerated graphics card.

The DVD MPEG2 decode card module supports viewing DVD video movies on a monitor connected to the 15-pin video output port on the PCI 2D/3D accelerated graphics card. DVD digital audio from the DVD media is sent to a DAC (digital-to-analog converter) and then to the Burgundy IC for analog stereo sound output to the currently selected sound output port.

#### CHAPTER 1

Introduction

#### Serial Modem Communications

An internal Apple 56 Kbps modem can be installed as an option at the time of purchase. The modem is compatible with K56flex, V.34, and V.90 protocols.

## **Compatibility Issues**

The Power Macintosh G3 computer incorporates several changes from earlier models. This section describes key issues you should be aware of to ensure that your hardware and software work properly.

#### System Software

The Power Macintosh G3 computer has a new system software architecture, called NewWorld, that provides Open Firmware booting and Mac OS Toolbox ROM in RAM. Mac OS 8.5 system software is installed on the startup drive. For more information, see Chapter 5, "System Software."

#### DMA Addresses and NewWorld Software

In the past, Macintosh computers that use the PCI bus had a one-to-one correspondence between physical addresses and logical addresses as long as VM was off. To allow DMA transfers with VM on, DMA device drivers made a call to the PrepareMemoryForIO function to set up physical and logical mapping for their memory buffers. On Macintosh computers that use the NewWorld software, DMA device drivers must always make that call, whether VM is on or off. Information about how to use the PrepareMemoryForIO function appears on pages 219–229 of *Designing PCI Cards and Drivers for the Power Macintosh*.

#### Machine Identification and NewWorld Software

The Power Macintosh G3 described in this note and other Macintosh computers that implement the NewWorld software architecture no longer have unique machine ID values. Applications cannot determine which computer they are running on by reading the Gestalt Manager gestaltMachineType values. If an application requires a name string value for the computer model, the application should instead check the name registry for the value of the

"Devices:device-tree:model" property to get a name string for the machine. The current model property string is "PowerMac1,1".

## No Graphics Support on MLB

The logic board in the Power Macintosh G3 computer does not include a built-in port for graphics output to an external monitor. Graphics output for the Power Macintosh G3 computer requires a PCI graphics card. A 2D/3D accelerated graphics card designed for the Power Macintosh G3 computer is installed in the 66 MHz PCI slot to support graphics output. For information about video monitors and the graphics card, see "Video Monitor Port" (page 55).

## No Built-in AV I/O Connectors

Composite video and S-Video connectors are not available on the Power Macintosh G3 computer. Digital video input and output features of the Power Macintosh G3 computer are provided by the FireWire ports and the built-in USB ports. The USB ports have a maximum speed of 12 Mbits per second and may not be suitable for video output to high-speed external storage devices.

The Power Macintosh G3 computer does not include RCA jacks for analog stereo audio input and output. The built-in 3.5 mm sound input and sound output connectors can be used for analog stereo audio input and output. Digital audio input and output associated with digital video are supported by the FireWire interface; see "FireWire Ports" (page 48).

## Modem Slot

The 70-pin modem connector in the Power Macintosh G3 computer is not the same as the connector on the modem slot in the original Power Macintosh G3 computers. The modem slot is strictly for Apple-designed modem cards.

## **PCI Expansion Slots**

The Power Macintosh G3 computer includes four PCI expansion slots. Three of the slots, slots B, C, and D (2, 3, and 4), are 5 V, 64-bit, 33 MHz slots that support both 32-bit and 64-bit PCI cards that are compliant with the PCI V2.1

#### CHAPTER 1

Introduction

specification. The other slot, slot A (1), is a 3.3 V, 32-bit, 66 MHz slot dedicated to a 2D/3D accelerated graphics card.

The 66 MHz PCI slot conforms to the PCI V2.1 specification with the exception that its clock speed is fixed at 66 MHz, so it does not accept 33 MHz cards. The 66 MHz PCI slot is keyed for 3.3 V only operation. Older 5 V cards cannot be installed in the 66 MHz PCI slot.

For more information, see "PCI Expansion Slots" beginning on page 66.

#### Internal Storage Devices

Standard configurations of the Power Macintosh G3 computer include two unused drive bays in the bottom of the enclosure. The factory installed drive is located in the back bay (bay 3). Bays are numbered 1 through 3 from front to back, as shown in Figure 1-4.

The drive bays accommodate 1-inch-high 3.5-inch devices. A PCI controller card is required for adding internal or external storage devices in addition to those in the three drive bays. For more information, see "Disk Drives" beginning on page 51.

#### **RAM Expansion**

The logic board uses JEDEC-standard SDRAM DIMM cards that are 64-bit bus, nonparity, 168-pin, 3.3-volt, unbuffered, and PC-100 compliant. The speed of the devices must be 125 MHz (8 ns).

#### IMPORTANT

DIMMs with any of the following features are not supported in the Power Macintosh G3 computer: registers or buffers, PLLs, ECC, parity, or EDO RAM. ▲

The maximum supported height of SDRAM DIMM cards is 2 inches. The maximum number of devices supported on a DIMM is 16 SDRAM devices. For information about SDRAM DIMM configurations, see "RAM DIMMs" (page 64).

## No L2 Cache Expansion

The backside L2 cache is integrated into the design of the microprocessor module. No cache expansion is possible without replacing the entire module.

## ATA-3 Drives

The CD-ROM, DVD-ROM, and ZIP drives are ATAPI devices, rather than SCSI devices. They are connected to the ATA-3 channel on the main logic board. The ATA Manager software supports PIO Mode 4 and DMA Mode 2 data transfers for devices on the ATA-3 channel.

## No SCSI Ports

The Power Macintosh G3 computer does not include built-in internal or external SCSI device connectors. Adding an internal or external SCSI device requires the use of a SCSI PCI card. Ultra2 SCSI (LVD) devices and PCI controller cards are standard in some configurations and are available as options at the time of purchase.

#### Line Voltages

The power supply is not self-configuring for different input voltages. The voltage switch is delivered preconfigured for the input voltage of the region in which the unit is originally purchased. If the computer is moved to another location where the input voltage is different, a voltage switch must be adjusted to accommodate the voltage change. The switch has two positions that support voltage ranges of 90 to 132 V or 180 to 264V.

#### Monitor Power

The monitor power socket is not switched. Any time power is connected to the power supply, power is available on the monitor power socket. A monitor that does not support energy-saving features that is connected to the monitor power socket does not power off when the computer is shut down. Monitors that do not support energy-saving features have to be switched manually.

## No Video RAM Expansion

The Power Macintosh G3 computer does not include built-in video RAM nor a slot for video RAM expansion on the main logic board. The accelerated graphics card that is installed in the computer includes 16 MB of SDRAM video memory and does not support video RAM expansion.

#### No LocalTalk Serial Ports

The Power Macintosh G3 computer does not include RS-422 LocalTalk serial ports found on earlier Macintosh models. Serial I/O for external USB devices is provided by two USB ports. USB adapters are available from third parties to support Macintosh-compatible legacy serial devices.

### **USB** Ports and Devices

The USB ports take the place of the serial I/O ports found on earlier Macintosh computers. Software shims have been implemented in the system software to allow existing applications that use ADB devices to work with USB devices.

The Power Macintosh G3 computer uses a USB keyboard and mouse similar to the USB keyboard and mouse introduced with the iMac computer.

USB game controllers are supported by the InputSprocket component of the Apple Games Sprockets software architecture. InputSprocket software and information about the InputSprocket APIs can be found at

http://developer.apple.com/dev/games/

# Architecture

#### CHAPTER 2

Architecture

This chapter describes the architecture of the main logic board and graphics expansion card. It describes the major components of the main logic board: the microprocessor and core ICs. Input and output connectors are discussed in Chapter 3, "I/O Features."

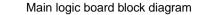

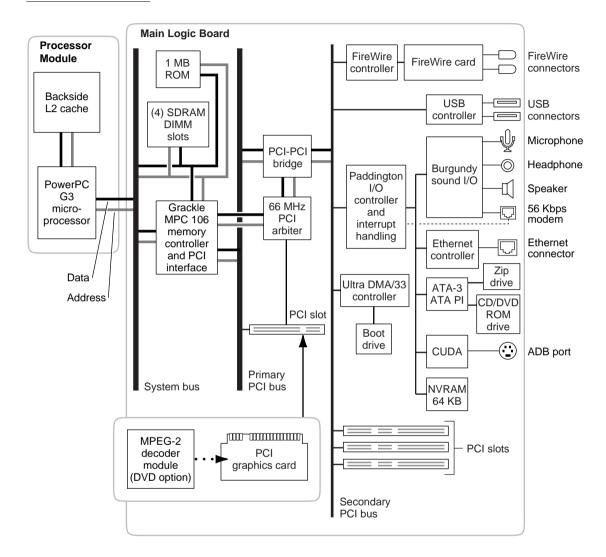

## **Block Diagram and Buses**

The architecture of the main logic board is based on the PowerPC G3 microprocessor and three buses: the processor bus and two PCI buses, a primary 32-bit 66 MHz bus and a secondary 64-bit 33 MHz bus. The processor bus connects the microprocessor, cache, and main memory; the primary PCI bus is for an Apple graphics card solution; the secondary PCI bus connects the I/O devices. The I/O devices on the secondary PCI bus are

- Ultra DMA/33 (ATA-4) disk interface

- USB interface

- FireWire interface

- Paddington I/O controller IC

- PCI 33.33 MHz 64-bit slots B (2), C (3), and D (4)

- DEC/Intel 21154 PCI-PCI bridge IC

Figure 2-1 shows the main logic board block diagram.

Architecture

Architecture

## Main Components

The following sections describe the principal electronic components on the computer's main logic board.

#### PowerPC G3 Microprocessor

The processor in the Power Macintosh G3 computer is a PowerPC 750 microprocessor running at 300 MHz, 350 MHz, or 400 MHz. Apple refers to these processors as PowerPC G3 microprocessors (G3 stands for "generation three").

The principal features of the PowerPC G3 microprocessor include

- full RISC processing architecture

- parallel processing units: load-store unit, two integer units, one complex integer unit, and one floating-point unit

- a branch manager that can usually implement branches by reloading the incoming instruction queue without using any processing time

- integrated L2 cache controller and Tag RAMs for high-performance memory access

- an internal memory management unit (MMU)

- 64 KB of on-chip cache memory (32 KB each for data and instructions)

For complete technical details, see the PowerPC Web pages at <a href="http://www.mot.com/SPS/PowerPC/index.html">http://www.mot.com/SPS/PowerPC/index.html</a> and <a href="http://www.chips.ibm.com/products/ppc/overview/">http://www.chips.ibm.com/products/ppc/overview/</a>.

The PowerPC G3 is located on a plug-in microprocessor card that includes the L2 cache.

#### Memory Subsystem

The memory subsystem consists of RAM and ROM on the main logic board as well as the backside second-level (L2) cache, which is located on a separate card

#### CHAPTER 2

#### Architecture

along with the microprocessor. The memory controller is described in "Grackle Memory Controller and PCI Bridge IC" (page 36).

#### Second-Level Cache

The backside second-level (L2) cache consists of 512 KB or 1 MB of SRAM. The cache is on the microprocessor card. The clock frequency of the cache is programmable and runs at one half the speed of the microprocessor, a ratio of 2:1. The L2 cache clock frequency can be divided down by 1, 1.5, 2, 2.5, or 3 from the core operating frequency of the PowerPC G3 microprocessor.

#### System ROM

With the NewWorld architecture, the system ROM consists of 1 MB of on-board ROM. It contains only the hardware specific code and tables needed to start up the computer, to load an operating system, and to provide common hardware access services. All the rest of the operaing system components that were formerly in ROM are now loaded from the boot device into RAM during the startup process. For a description of the ROM in the NewWorld architecture, refer to "Boot ROM Contents" (page 74).

#### System RAM

Four DIMM sockets are used for main memory. The DIMM sockets support SDRAM devices on 168-pin JEDEC-standard 3.3-volt unbuffered PC-100 SDRAM DIMMs. Supported DIMM sizes are 8, 16, 32, 64, 128, and 256 MB. The Grackle IC provides memory control for the system RAM. For more information, see "RAM DIMMs" (page 64).

#### Core ICs

The architecture of the main logic board is designed around five integrated circuits:

- the Grackle (MPC 106 v4) memory controller and PCI bus bridge

- DEC/Intel 21154 PCI-PCI bus bridge

- the Paddington I/O subsystem and DMA controller

- the Burgundy sound processor

- the Cuda soft-power controller

#### Architecture

• the ATI 3D RAGE 128 GL video subsystem (on the accelerated graphics card)

The computer also uses several standard ICs for I/O support, which include the Ultra DMA/33 controller, the FireWire controller, and the USB controller. This section describes only the core ICs.

#### Grackle Memory Controller and PCI Bridge IC

The Grackle IC functions as the bridge between the PowerPC microprocessor bus and the I/O and graphics devices on the PCI buses. It provides buffering and address translation from one bus to the other.

The Grackle IC also provides the control and timing signals for ROM and RAM. The memory control logic supports byte, word, longword, and burst accesses to the system memory. If an access is not aligned to the appropriate address boundary, Grackle generates multiple data transfers on the bus.

#### **Memory Control**

The Grackle IC controls the system RAM and ROM and provides address multiplexing and refresh signals for the DRAM devices. For information about address multiplexing, see "RAM Address Multiplexing" (page 65).

#### **PCI Bus Bridges**

The Grackle IC acts as a bridge between the processor bus and the PCI expansion buses, converting signals on the PCI bus to the equivalent signals on the processor bus and vice-versa. The PCI bridge functions are performed by two converters. One accepts requests from the processor bus and presents them to the PCI bus. The other converter accepts requests from the PCI bus and provides access to the RAM and ROM on the processor bus.

The PCI bus bridge in the Grackle IC runs synchronously. The processor bus operates at a clock rate of 100 MHz, the primary PCI bus operates at 66.67 MHz and the secondary PCI bus at 33.33 MHz. A Dec/Intel 21154 PCI-to-PCI bus bridge IC synchronizes transactions on the primary and secondary PCI buses for the Grackle IC. Primary PCI bus arbitration is performed by the Apple Gated Clocks II IC. The PCI-to-PCI bridge IC performs arbitration services for the secondary PCI bus.

The PCI bus bridge generates PCI parity as required by the PCI bus specification, but it does not check parity or respond to the parity error signal.

#### Paddington I/O Controller IC

The Paddington IC is an enhanced I/O controller and DMA engine for Power Macintosh computers using the PCI bus architecture. The Paddington IC in the Power Macintosh G3 is an improved version of the Paddington IC used in the iMac computer. The primary change is improved performance with 100 Mbps Ethernet. The changes are for internal operation and are transparent to software.

Paddington also provides power-management control functions for energy saving features included on Power Macintosh computers. The Paddington IC is connected to the secondary PCI bus and uses the 33 MHz PCI bus clock.

The Paddington IC includes circuitry equivalent to the Ethernet, ATA-3, SCC, and VIA controller ICs. The functional blocks in the Paddington IC include the following:

- systemwide interrupt handling

- ATA-3 interface controller

- sound control logic and buffers

- 10/100 twisted-pair Ethernet controller

The Paddington IC provides bus interfaces for the following I/O devices:

- 56K modem card

- VIA system interface to the Cuda IC

- Burgundy sound input and output IC

- 64 KB nonvolatile RAM control

The Paddington IC also contains a serial interface and sound control logic for the Burgundy sound IC. The optional 56 Kbps modem uses the serial interface.

#### **Burgundy Sound IC**

The Burgundy sound IC combines a 16-bit digital sound encoder and decoder (codec). The Burgundy IC has the following sound controller features:

- Digitizes analog inputs with internal analog to digital converters (A/Ds).

- Creates analog outputs with internal digital to analog converters (DACs).

- Facilitates digital audio routing between the inputs and outputs and CPU.

- Provides digital gain, fade, balance, and mute controls.

- Provides digital tone control.

For additional information about the audio features, see "Sound System" (page 53).

### Cuda IC

The Cuda IC provides several system functions, including

- management of soft system resets

- management of the real-time clock

- software control of the power supply

- I<sup>2</sup>C bus control for Cuda (master), four DIMM slots, and clock buffer

## **Graphics Controller IC**

The ATI 3D RAGE 128 GL graphics controller IC on the accelerated graphics card contains the logic for the video display. The ATI 3D RAGE 128 GL graphics controller includes the following features:

- advanced 128-bit rendering engine

- architecture optimized to support high-speed SDRAM video memory

- display memory controller, built-in drawing coprocessor, video scaler, color space converter, clock generator, and true color palette video DAC (digital-to-analog converter)

- video CLUT (color lookup table)

- hardware graphics acceleration with a 16-bit Z-buffer

- accelerated QuickDraw 3D rendering up to six times that of software-only acceleration

- true color palette DAC supporting pixel clock rates to 200 MHz for 1600 by 1200 resolution at 90 Hz

- graphics and video line buffer for superior video scaling and playback quality

- hardware cursor up to 64 x 64 x 2

- DDC1 and DDC2B+ for plug-and-play monitor support

■ graphics control accessible through the QuickDraw, QuickDraw 3D, QuickDraw 3D RAVE, and QuickTime APIs

A separate data bus handles data transfers between the ATI 3D RAGE 128 GL graphics controller and the display memory. The display memory data bus is 64 bits wide, and all data transfers consist of 64 bits at a time. The RAGE IC breaks each 64-bit data transfer into several pixels of the appropriate size for the current display mode—4, 8, 16, 24, or 32 bits per pixel.

The ATI 3D RAGE 128 GL graphics controller IC uses several clocks. Its transactions are synchronized with the PCI bus. Data transfers from the frame-buffer RAM are clocked by the MEM\_CLK signal. Data transfers to the CLUT and the video output are clocked by the dot clock, which has a different rate for different display monitors.

The 2D graphics accelerator is a fixed-function accelerator for rectangle fill, line draw, polygon fill, panning/scrolling, bit masking, monochrome expansion, and scissoring.

## **Display Memory**

The display memory on the accelerated graphics card is separate from the main memory. The display memory consists of 16 MB of 100 MHz/10 ns SDRAM devices configured to make a 64-bit data bus. The display memory cannot be expanded.

With the 16 MB of video memory, the display data generated by the computer can have pixel depths of 8, 16, or 32 bits for monitors up to1920 by 1080 pixels. For a complete listing of the display resolutions, see "Display Resolution Modes" (page 59).

## **USB** Controller

The USB controller is a standard USB controller IC with two USB connectors that support USB devices with data transfer rates of 1.5 Mbps or 12 Mbps. The register set complies with the Open Host Controller Interface (OHCI) specification.

## FireWire Link Controller

The Texas Instruments PCI-Lynx FireWire controller IC supports the IEEE 1394 FireWire high-speed serial interface standard at 100, 200, and 400 Mbps. It provides the link interface layer to the FireWire physical layer on the FireWire card.

## **Optional Internal Modem**

The optional internal hardware modem is a separate module that is connected to the SCC port A of the Paddington IC. The module contains a modem controller IC, a data pump, and the interface to the telephone line (DAA).

I/O Features

This chapter describes both the built-in I/O devices and the ports for connecting external I/O devices. Each of the following sections describes an I/O port or device.

# **ADB** Port

The Power Macintosh G3 computer has an Apple Desktop Bus (ADB) port for ADB devices and ColorSync control of Apple monitors. The ADB port is functionally the same as on other Macintosh computers. The connector is located on the back of the computer.

The ADB connector is a 4-pin mini-DIN connector. Figure 3-1 shows the arrangement of the pins on the ADB connector.

Figure 3-1 ADB connector

The ADB is a single-master, multiple-slave serial communications bus that uses an asynchronous protocol and connects keyboards, graphics tablets, mouse devices, and other devices to the computer. The custom ADB microcontroller drives the bus and reads status from the selected external device. For more information about the ADB, see *Guide to the Macintosh Family Hardware*, second edition.

#### IMPORTANT

The total current available for all devices connected to the +5 V pins on the ADB is 100 mA.  $\blacktriangle$

```

CHAPTER 3

```

|               | ADB conne |                                                                                                                                                            |  |  |

|---------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>number | Name      | Description                                                                                                                                                |  |  |

| 1             | ADB       | Bidirectional data bus used for input and output; an<br>open collector signal pulled up to +5 volts through a<br>470-ohm resistor on the main logic board. |  |  |

| 2             | PSW       | Power-on signal; generates reset and interrupt key combinations.                                                                                           |  |  |

| 3             | +5V       | +5 volts from the computer.                                                                                                                                |  |  |

| 4             | GND       | Ground from the computer.                                                                                                                                  |  |  |

#### Table 3-1 ADB connector pin assignments

# **USB** Ports

The Power Macintosh G3 computer has two Universal Serial Bus (USB) ports that are used to connect the keyboard and mouse as well as additional I/O devices such as printers, scanners, and low-speed storage devices.

For more information about USB on Macintosh computers, please refer to Apple Computer's *Mac OS USB DDK API Reference*. Information is also available on the World Wide Web, at

http://developer.apple.com/dev/usb/

For full specifications of the Universal Serial Bus, refer to the USB Implementation Forum on the World Wide Web, at

http://www.usb.org/developers/index.html

## **USB** Connectors

The USB ports use USB Type A connectors, which have four pins each. Two of the pins are used for power and two for data. Table 3-2 shows the pin assignments.

#### Table 3-2 USB connector pin assignments

| Pin | Signal<br>name | Descripti<br>on |

|-----|----------------|-----------------|

| 1   | VCC            | +5 VDC          |

| 2   | D-             | Data –          |

| 3   | D+             | Data +          |

| 4   | GND            | Ground          |

The USB ports support both low-speed and high-speed data transfers, at 1.5 Mbits per second and 12 Mbits per second, respectively.

## Transfer Types Supported

The USB specification defines four data transfer types:

- Control transfers, used for device configuration and initialization.

- Bulk transfers, used for printers, scanners, modems, and other devices that require accurate delivery of data with relaxed timing constraints.

- Interrupt transfers, used for human interface device (HID) class devices such as keyboards and mice, as well as devices that report status changes, such as serial or parallel adaptors and modems.

- Isochronous transfers, used for on-time delivery of data. Isochronous data transactions are best suited for audio or video data streams.

Version 1.1 of the Macintosh USB system software (the version that comes with the Power Macintosh G3) provides functions that support all four transfer types. The earliest version did not support isochronous transfers; if your software requires them, it should make a Gestalt call to determine whether they are supported.

## **USB** Compatibility Issues

The USB ports augment the ADB ports and take the place of the serial I/O ports found on earlier Macintosh computers, but they do not function the same way. The following sections describe the differences.

#### **ADB** Compatibility

Apple is providing an ADB/USB shim to support processes that control ADB devices by making calls to the ADB Manager and the Cursor Device Manager. The ADB/USB shim makes it possible for processes that support an ADB keyboard to work with the USB keyboard equivalent.

For example, the ADB/USB shim allows applications to set the Caps Lock and Num Lock LEDs on the Apple USB keyboard. The ADB/USB shim also allows the Cursor Device Manager to support a USB mouse.

Keyboards other than the Apple USB keyboard can be used with the Power Macintosh G3 computer, but they will be treated as having an ADB device ID of 2.

#### IMPORTANT

The ADB/USB shim does not support USB devices other than the keyboard and mouse.  $\blacktriangle$

#### Note

The ADB/USB shim is built into the Mac OS ROM image on the Power Macintosh G3 computer, as it is on all Power Macintosh systems that have USB ports. ◆

#### Serial Port Compatibility

The first release of the Mac OS USB DDK does not include a universal Serial/ USB shim that would allow processes that use the Communications Toolbox's Communications Resource Manager (CRM) to find and use a USB modem device. Any USB modem device would need to implement its own communication shim to provide an interface between the CRM and its USB Communication class driver.

For more information, please refer to the Mac OS USB DDK, which is available from the Apple Developer DDK page on the World Wide Web, at

http://developer.apple.com/sdk/

I/O Features

#### Macintosh-To-Macintosh Connections

USB is a serial communications channel, but it does not replace LocalTalk networking on Macintosh computers; you cannot connect two Macintosh computers using the USB. The best method for networking Power Macintosh G3 computers is through the built-in Ethernet port.

## **USB Storage Devices**

The Macintosh USB software does not support booting from an external USB storage device.

## **USB** Controller

The Power Macintosh G3 computer uses an Open Host Controller Interface (OHCI) controller for USB communication. Some early USB devices (most notably keyboards) can't interoperate with an OHCI controller. Those devices are not supported by the Macintosh USB system software.

# Keyboard

The Power Macintosh G3 computer comes with an Apple USB keyboard.

A keyboard extension cable (part number 590-2244) is provided for installations where the computer is located on the floor or away from the immediate desktop area. The extension cable is a special cable that is keyed to work with the Apple USB keyboard. The combined keyboard and extension cable has been tested as a complete system.

## **Keyboard Layout**

The Apple USB keyboard has a total of 82 keys, including 12 function keys, a numeric keypad, and a set of 4 cursor-control keys. The cursor-control keys are in the inverted-T arrangement.

There are three versions of the Apple USB keyboard used in different parts of the world: ANSI (North America), JIS (Japan), and ISO (Europe). Figure 3-2 shows the keyboard layout for the ANSI keyboard. Applications can determine

I/O Features

which keyboard is connected by calling the Gestalt Manager and checking for the corresponding value of the gestaltKeyboardType selector:

- gestaltUSBCosmoANSIKbd (value = 198)

- gestaltUSBCosmoJISKbd (value = 200)

- gestaltUSBCosmoISOKbd (value = 199)

Power to the computer can be turned on using the power button on the Apple USB keyboard. A proprietary circuit allows the power control circuitry on the main logic board to detect a power-button press and turn on the power. The Apple USB keyboard can be used to turn on the power only if the keyboard is connected directly to the computer or is connected to an Apple Studio Display with a USB hub that is connected directly to the computer.

The standard NMI and reset key combinations are supported, but the keys are decoded in software and may not be available under some crashed conditions. Therefore, NMI and reset switches are also available on the front of the computer.

## Keyboard and USB

The Apple USB keyboard is designed to work with the computer by way of the USB ports. The keyboard has a captive cable with a USB Type A connector. The keyboard is a bus-powered USB hub with two USB Type A ports. The ports support transfer rates up to 12 Mbps.

I/O Features

#### 🔺 WARNING

A bus-powered hub as defined in the USB specification does not provide enough power to support a second bus-powered hub. A second bus-powered hub must be connected to the second USB port on the computer, not to a port on the Apple USB keyboard. ▲

Apple provides a HID class driver for the Apple USB keyboard, which supports the USB boot protocol. Other keyboards intended for use on the Macintosh platform must support the HID boot protocol, as defined in the USB Device Class Definition for Human Interface Devices (HIDs).

## Mouse

The Apple USB mouse is designed to work with the computer by way of the USB ports. The mouse case is round and has the same two-tone color design as the case of the computer. The Apple USB mouse operates as a low-speed (1.5 Mbps) USB device.

The mechanism inside the Apple USB mouse is similar to that in the Apple Desktop Bus Mouse II. The mouse ball is removeable for cleaning; the ring that allows access to the ball can be locked by inserting an unfolded paper clip into a small hole and turning the ring clockwise.

# **FireWire Ports**

The computer includes two external FireWire IEEE 1394 ports on the rear panel of the enclosure. The features of the FireWire ports are:

- support high-speed serial I/O at 100, 200, and 400 Mbps

- provide 15 watts of power when the computer system is on

- accept external power input on FireWire bus when system is off

The FireWire hardware and software provided with the computer are capable of all asynchronous and isochronous transfers defined by IEEE standard 1394-1995. Developers of FireWire peripherals are required to provide device drivers.

I/O Features

It is possible to connect two computers to each other using a FireWire cable, but no software is provided to make use of such a connection. Also, third-party software such as video editing applications may not deal gracefully with a shared FireWire peripheral if two or more computers attempt to communicate with it at the same time.

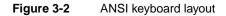

## **FireWire Connector**

The FireWire connector has six contacts, as shown in Figure 3-3. The connector pin assignments are shown in Table 3-3.

Figure 3-3 FireWire connector

Table 3-3

FireWire connector pin assignments

| Pin | Signal<br>name | Description                                    |

|-----|----------------|------------------------------------------------|

| 1   | Power          | Unregulated DC; 24 V no load                   |

| 2   | Ground         | Ground return for power and inner cable shield |

| 3   | TPB-           | Twisted-pair B, differential signals           |

| 4   | TPB+           |                                                |

| Table 3-3 | FireWire connector pin assignments |

|-----------|------------------------------------|

|-----------|------------------------------------|

| Pin   | Signal<br>name | Description                          |

|-------|----------------|--------------------------------------|

| 5     | TPA-           | Twisted-pair A, differential signals |

| 6     | TPA+           |                                      |

| Shell | —              | Outer cable shield                   |

The power pin provides a maximum voltage of 24 V (no load) and up to 15 W total power on both connectors. When the computer is off, the power pin accepts external power at 8 to 33 V, in conformity with the P1394a draft standard.

Pin 2 of the 6-pin FireWire connector is ground for both power and inner cable shield. If a 4-pin connector is used on the other end of the FireWire cable, its shell should be connected to the wire from pin 2.

The signal pairs are crossed in the cable itself so that pins 5 and 6 at one end of the cable connect with pins 3 and 4 at the other end. When transmitting, pins 3 and 4 carry data and pins 5 and 6 carry clock; when receiving, the reverse is true.

For additional information about the FireWire interface and the Apple APIs for FireWire device control, refer to the resources available on the Apple FireWire Web site at

http://devworld.apple.com/dev/FireWire/index.html

or send electronic mail to

firewire@apple.com

# **Ethernet Port**

The Power Macintosh G3 computer has a built-in 10/100 Mbps Ethernet port. The user can connect it to either a 10Base-T or a 100Base-TX hub; the port automatically senses which type of hub is connected.

The connector for the Ethernet port is an RJ-45 connector on the back of the computer.

The Ethernet interface in the Power Macintosh G3 computer conforms to the ISO/IEC 802.3 specification, where applicable.

# **Internal Modem**

The Power Macintosh G3 computer includes an option for an internal modem. The modem interface to the main logic board is a 70-pin connector. The external I/O connector for the modem is an RJ-11 connector located on the back of the computer. The modem has the following features:

- modem bit rates up to 56 Kbps (supports K56flex, V.34, and V.90 protocols)

- fax modem bit rates up to 14.4 Kbps

The modem appears to the system as a serial port that responds to the typical AT commands. The modem provides a sound output for monitoring the progress of the modem connection.

#### Note

This developer note does not provide the electrical or mechanical specifications for the 70-pin modem interface to the main logic board.

# **Disk Drives**

The Power Macintosh G3 computer has an Ultra DMA/33 (ATA/ATAPI-4) interface and an ATA-3 interface for internal mass storage and removable media devices. The enclosure includes data and power connectors for the boot drive on the Ultra DMA/33 interface. It also includes data and power connectors for an optional internal ATAPI CD-ROM or DVD-ROM drive and an internal ATAPI ZIP drive. Those drives are connected to the ATA-3 interface.

The enclosure also includes two additional drive bays for other mass storage devices connected to an optional or user-installed controller card in a PCI slot. None of the drive bays can be modified to support removable drive bay kits. The locations of the drive bays are shown in Figure 1-4.

#### I/O Features

The Ultra DMA/33 bus supports PIO Mode 4, DMA Mode 2, and Ultra DMA Mode 2 data transfers. The ATA-3 bus supports PIO Mode 4 and DMA Mode 2 data transfers.

The ATA-3 channel supports two ATA devices. The devices are configured in a ATA Device 0/1 configuration. The ATAPI CD or DVD-ROM and Zip drive, when installed, occupy both device locations on the ATA-3 channel. The ATAPI CD or DVD-ROM, depending on which is installed, is Device 0 (master), and the Zip drive is Device 1 (slave). If the Zip drive is not factory installed in the system, a power and data cable is available for adding a Zip drive to the ATA-3 bus in the Zip drive bay. The device has to be device-select jumpered as Device 1 (slave).

The Power Macintosh G3 computer does not include a 1.44 MB floppy drive.

## Ultra DMA/33 Hard Disk Drive

The logic board supports an internal hard disk drive that uses the Ultra DMA/33 (ATA/ATAPI-4) interface. The Power Macintosh G3 comes with an Ultra DMA/33 hard disk or an Ultra2 SCSI hard disk installed in Slot 3.

The internal hard disk drive has a 40-pin connector and a separate 4-pin power connector. An 80-conductor high-density cable with a 40-pin connector is attached to the main logic board. To provide improved signal quality, the 80-conductor cable provides a separate ground for each of the signals on the 40 pin connector. The separate power cable is attached directly to the power supply.

## Optional Ultra2 SCSI (LVD) Drive

An optional Ultra2 SCSI (LVD) disk drive and Ultra2 SCSI (LVD) PCI controller card are available as a configuration option. The Ultra2 SCSI (LVD) interface provides data transfer rates of up to 80 MB per second. Additional information about the Ultra2 SCSI (LVD) interface can be found at:

http://www.quantum.com/src/whitepapers/

## ATAPI CD-ROM Drive

The Power Macintosh G3 computer has a 24x-speed internal ATAPI CD-ROM drive. The CD-ROM drive supports the worldwide standards and specifications

for CD-ROM and CD-digital audio discs described in the Sony/Philips Yellow Book and Red Book. The drive can read CD-ROM, CD-ROM XA, CD-I, and PhotoCD discs as well as play standard audio discs.

The CD-ROM drive has a sliding tray to hold the disc. The drive features a mechanism that supports 4x, 8x, 12x, and 24x data transfer rates and a data buffer that further enhances performance. The CD is connected as device 0 in a ATA Device 0/1 configuration.

## **Optional ATAPI Zip Drive**

The Zip drive is an ATAPI drive and is connected as device 1 in an ATA Device 0/1 configuration on the ATA-3 channel of the main logic board.

## **Optional DVD-ROM Drive**

The optional DVD-ROM drive is fully compatible with existing CD-ROM media. The drive supports CD-ROM at 32x speed maximum and DVD at 5x constant linear velocity (CLV). The DVD-ROM drive supports the following disc formats:

- DVD-ROM (One-layer or two-layer, one-sided or two-sided)

- CD-ROM (Modes 1 and 2), CD-ROM XA (Mode 2, Forms 1 and 2), CD-Audio, Photo CD, CD-RW, CD-R, CD-Extra

- CD-I (Mode 2, Forms 1 and 2), CD-I Ready, CD-I Bridge

- Video CD

# Sound System

The sound system for the Power Macintosh G3 computer supports 44.1 kHz 16-bit stereo sound output and input, available simultaneously.

Like other AV class Macintosh computers, the sound circuitry and system software can create sounds digitally and either play the sounds through speaker inside the enclosure or send the sound signals out through the sound output jack. The Power Macintosh G3 computer also records sound from several sources: an analog sound source connected to the line-level sound input jack,

analog sound from the modem card connected to the internal modem connector, or a compact disc in the CD-ROM player. With each sound input source, sound playthrough can be enabled or disabled.

## Sound Outputs

The Power Macintosh G3 computer provides one 3.5-mm mini jack for sound output on the back of the enclosure.

The output jack is connected to the sound amplifier; the mini jack is intended for connecting a pair of headphones or amplified external speakers. Inserting a plug into the sound output mini jack disconnects the built-in speaker. The computer has one built-in speaker.

The Burgundy IC provides the stereo sound output to both the internal speakers and the sound output jack.

The sound output jack has the following electrical characteristics:

- output sound signal to noise ratio (SNR) <90 dB unweighted (typical) when sound playback is from system hard disk drive or main memory

- output sound SNR <80 dB unweighted (nominal) when playback is from CD

- overall output sound SNR <90 dB unweighted (typical)

## Sound Inputs

The Power Macintosh G3 computer provides a stereo sound input jack on the back of the enclosure for connecting an external PlainTalk microphone or other sound source. The sound input jack accepts a standard 3.5-mm stereophonic phone plug (two signals plus ground).

#### Note

The Apple PlainTalk microphone requires power from the main computer, which it obtains by way of an extra-long, 4-conductor plug that makes contact with a 5-volt pin inside the sound input jack. ◆

The sound input jack has the following electrical characteristics:

- input impedance: 20 k $\Omega$

- maximum input level without distortion: 2.5 V peak to peak (Vpp) maximum

- line-level microphone voltage range of 0.28 V to 2.1 V peak to peak

- input SNR <90 dB unweighted (typical) for recording to system hard disk drive or main memory

## **Digitizing Sound**

The sound circuitry digitizes and records sound as 44.1 kHz 16-bit samples. If a sound sampled at a lower rate on another computer is played as output, the Sound Manager transparently upsamples the sound to 44.1 kHz prior to outputting the audio to the Burgundy sound IC.

When recording sound from a microphone, applications that are concerned about feedback should disable sound playthrough by calling the Sound Manager APIs.

The Burgundy IC provides separate sound buffers for input and for stereo output so that the computer can record and send digitized sound to the sound outputs simultaneously.

# Video Monitor Port

The Power Macintosh G3 computer has a built-in accelerated graphics card that provides the port for the external video monitor.

## **Graphics Card**

The accelerated graphics card in the Power Macintosh G3 computer has the following features:

- 128-bit 2D/3D graphics and multimedia accelerator IC, the ATI 3D RAGE 128 GL

- 16 MB of synchronous dynamic RAM (SDRAM) soldered to the card (no video RAM expansion)

- hardware acceleration of 2D QuickDraw graphics and video to speed up scrolling text and graphics and screen redraw operations

- hardware acceleration of video for full screen, full motion, TV-quality playback of Cinepak and MPEG1 QuickTime movies

- connector for the DVD decode module supporting the playback of DVD video

- bilinear hardware interpolation and scaling

- accelerated 3D QuickDraw rendering up to six times that of software-only rendering

- real-time 3D shaded object manipulation, animation, and virtual world navigation

- 16-bit Z buffer for hidden texture surface removal

- six perspectively correct texture mapping functions

- alpha blending, transparency, and fog effects

- flat and Gouraud shading

- video textures and video lighting

The graphics acceleration features enhance the realism of 3D interactive application software and games.

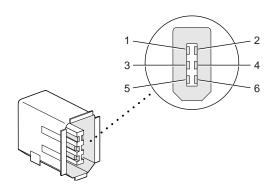

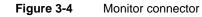

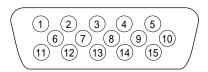

## **Monitor Connector**

The monitor connector is a standard DB9/15 (also called mini sub D15) connector for use with a VGA, SVGA, or XGA monitor. Figure 3-4 shows the pin configuration and Table 3-4 lists the signal pin assignments.

#### Table 3-4 Monitor connector pin assignments

| Pin     | Signal name | Description                       |

|---------|-------------|-----------------------------------|

| 1       | RED         | Red video signal                  |

| 2       | GREEN       | Green video signal                |

| 3       | BLUE        | Blue video signal                 |

| 4       | MONID(0)    | Monitor ID signal 0               |

| 5       | GND         | DDC return                        |

| 6, 7, 8 | AGND_VID    | Analog video ground               |

| 9       | +5V_IO      | 5 V power for I/O device          |

| 10      | GND         | HSYNC and VSYNC ground            |

| 11      | VGA_ID      | VGA ID signal                     |

| 12      | MONID(2)    | Monitor ID signal 2               |

| 13      | HSYNC       | Horizontal synchronization signal |

| 14      | VSYNC       | Vertical synchronization signal   |

| 15      | MONID(1)    | Monitor ID signal 1               |

## **Monitor Adapter**

An monitor adapter (included with the computer) allows the user to connect a standard Apple monitor cable to the computer. The adapter enables the computer to recognize a wide range of monitor types. The Apple part number for the adapter is 590-1120.

## **Monitor Sense Codes**

To identify the type of monitor connected, the computer first determines whether the adapter is connected. It does this by checking pin 11; on the new adapter, this pin is connected to the VSYNC signal. If the adapter is not found, the computer next checks to determine whether a DDC-type monitor is connected. DDC is the interface that provides monitor ID signals for VGA and SVGA monitors.

If the computer does not detect a DDC-capable monitor, it uses the Apple monitor sense codes on the signals MONID(0-2) in Table 3-4. Table 3-5 shows the sense codes and the extended sense codes for each of the monitors the card can support.

#### Note

The Apple Studio Display 17"/viewable 16" is listed in Table 3-5 with sense code value \$06-23, but it is identified using DDC on most Macintosh computers. ◆

| Monitor type                                                               | Standard sense code Extended sense code |        |        |        |

|----------------------------------------------------------------------------|-----------------------------------------|--------|--------|--------|

|                                                                            | (S2–0)                                  | (S1,0) | (S2,0) | (S2,1) |

| Macintosh 21-inch Color Display                                            | 000                                     | —      | —      | —      |

| Macintosh Portrait Display                                                 | 001                                     | —      | —      | —      |

| Macintosh 12-inch RGB Display                                              | 010                                     | —      | —      | —      |

| Apple Two-Page Monochrome Monitor                                          | 011                                     | —      | —      | —      |

| NTSC monitor                                                               | 100                                     | —      | —      | —      |

| 15-inch RGB monitor                                                        | 101                                     | —      | —      | —      |

| Apple Multiple Scan 14 or 15 Display                                       | 110                                     | 0 0    | 0 0    | 11     |

| Apple Multiple Scan 17 or 1705 Display                                     | 110                                     | 0 0    | 10     | 11     |

| Apple Studio Display 17"/viewable 16" or<br>Apple Multiple Scan 20 Display | 110                                     | 10     | 0 0    | 11     |

#### Table 3-5Monitor sense codes

| Table 3-5 | Monitor sense codes | (continued)  |

|-----------|---------------------|--------------|

|           |                     | (containada) |

| <b>Monitor type</b><br>Apple Studio Display 15", AppleStudio<br>Display 21" with Colorsynch technology,<br>AppleVision 850, 850av, 1710, and 1710av<br>Displays, Macintosh 12-inch Monochrome<br>Display, or AppleColor High Resolution<br>RGB Monitor | Standard<br>sense code<br>1 1 0 | Extended<br>1 0 | sense code<br>1 0 | 11  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|-------------------|-----|

| PAL monitor                                                                                                                                                                                                                                            | 111                             | 0 0             | 0 0               | 0 0 |

| NTSC monitor, with convolution                                                                                                                                                                                                                         | 111                             | 01              | 01                | 0 0 |

| VGA or SVGA monitor                                                                                                                                                                                                                                    | 111                             | 01              | 01                | 11  |

| Macintosh 16-inch Color Display                                                                                                                                                                                                                        | 111                             | 10              | 11                | 01  |

| PAL monitor, with convolution                                                                                                                                                                                                                          | 111                             | 11              | 0 0               | 0 0 |

| 19-inch RGB monitor                                                                                                                                                                                                                                    | 111                             | 11              | 10                | 10  |

| No monitor connected                                                                                                                                                                                                                                   | 111                             | 11              | 11                | 11  |

For a complete description of the sense code system, refer to Technote HW 30 *Sense Lines.* To find out how to obtain Apple Technical Notes, see "Supplemental Reference Documents" (page 12).

## **Display Resolution Modes**

When power is applied, the monitor is initially set for a display size of 640 by 480 pixels. With a multisync monitor the user can switch the monitor resolution on the fly by using the BitDepths and Resolutions modules in the control strip or the Monitors & Sound control panel.

Table 3-6 shows the display resolution, vertical and horizontal scan rates, and maximum pixel depths supported by the accelerated graphics card with the ATI 3D RAGE 128 GL graphics controller. The 16 MB of video RAM on the

accelerated graphics card supports pixel depths up to 32 bits per pixel at all resolutions.

## Table 3-6 Supported display resolutions

| Display                  | Vertical<br>scan | Horizonta<br>I |